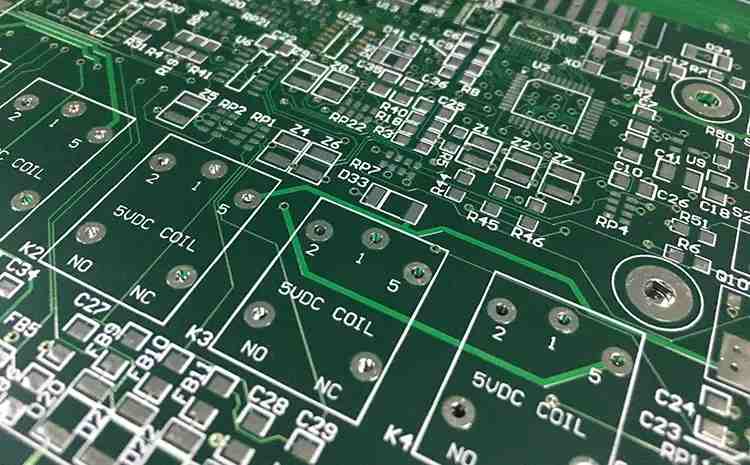

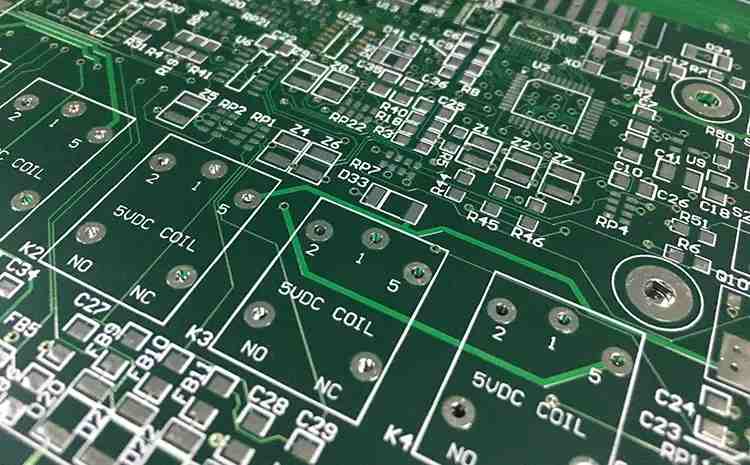

Circuit board assembly manufacturers explain the new challenges faced by high-speed and high-density PCB design: system level consideration of high-speed problems

When the system develops from hundreds of megabytes to tens of gigabytes, chip design, package design and system design can no longer be considered separately. For high-end products, packaging design and system design should be considered when designing chips.

After removing the problems of the software itself, how to streamline the process, reduce engineers' mistakes in the process, enable engineers to put more energy into the design, and enable products to enter the market as soon as possible has also become the content that EDA manufacturers are considering.

Usually, the connecting line on a system starts from the I/O of the Silicon, goes through the bump and subset of the package, reaches the encapsulated pin, and then goes through the PCB to the other encapsulated pin, subset, bump and I/O of the chip. Chips, packages, and circuit boards are three different areas. Previous engineers did not consider them comprehensively when designing, nor did they know what other engineers thought. However, with the increase of design frequency, the reduction of chip area, and the shortening of design cycle, manufacturers should take packaging design and PCB design into account when designing chips to effectively combine the three. Chen Lanbing said, "At this time, whether from the perspective of signal integrity or design cycle, we should consider the design of Silicon Package Board at the same time and coordinate their interrelationships. For example, sometimes there are timing problems that are difficult to solve in PCB, but they can be easily solved in Package."

Cadence, as an active advocate of system level process design, its Allegro platform covers board level design and package level design, and can be connected with several other chip design platforms of Cadence to form a complete design chain and realize effective data exchange and communication. In addition, Cadence's VSIC (Virtual System InterConnect) design method is a new Silicon Package Board collaborative design method, which enables engineers to consider timing or signal integrity problems caused by the entire system at the early stage of design, and solves a major bottleneck in the design of gigahertz signals. Circuit board assembly and circuit board processing manufacturers explain the new challenges faced by high-speed and high-density PCB design: high-speed considerations at the system level