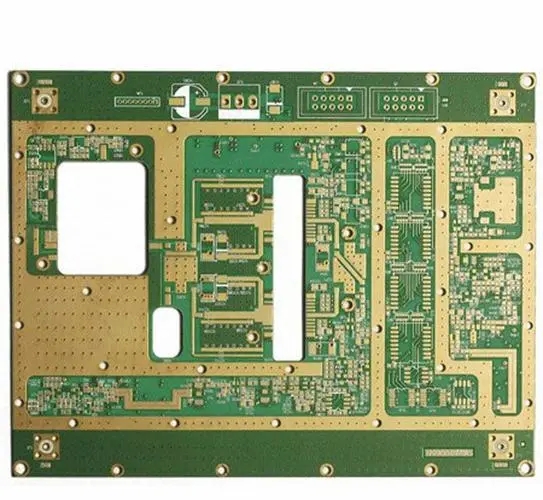

Oxidation Analysis of Gold Deposited PCB and Problems of Multilayer PCB

Basis for selecting the width of printed wire: the minimum width of printed wire is related to the current flowing through the wire: if the line width of PCB is too small, and the resistance of rigid printed wire is large, the voltage drop on the line will be large, which will affect the circuit performance of PCB. If the line width is too wide, the wiring density is not high, and the area of PCB increases, which is not conducive to miniaturization in addition to increasing costs If the current load is calculated by 20A/mm2, when the thickness of copper clad foil is 0.5MM, the current load of 1MM (about 40MIL) line width is 1A. Therefore, the line width of 1 – 2.54MM (40 – 100MIL) can meet the general application requirements. The line width of the ground wire and power supply on the high-power equipment board can be appropriately increased according to the power size, while on the low-power digital circuit, in order to improve the wiring density, The minimum line width is 0.254 – 1.27MM (10 – 15MIL). In the same circuit board, the power line and ground wire are thicker than the signal line.

2. The line spacing of PCB board: when the line spacing is 1.5 mm (about 60 MIL), the insulation resistance between lines is greater than 20 M Ω, and the maximum withstand voltage between lines can reach 300 V. When the line spacing is 1 mm (40 MIL), the maximum withstand voltage between lines is 200 V. Therefore, on the circuit board of medium and low voltage (the line to line voltage is not greater than 200 V), the line spacing is 1.0 – 1.5 mm (40-60 MIL). In low-voltage circuits, such as digital circuit systems, it is not necessary to consider the breakdown voltage, as long as the production process allows, it can be very small.

3. Pad: For a resistance of 1/8W, the lead diameter of the pad is 28MIL, while for a resistance of 1/2W, the lead diameter is 32MIL, the lead hole is too large, and the width of the copper ring of the pad is relatively reduced, resulting in a decrease in the adhesion of the pad. It is easy to fall off, the lead hole is too small, and it is difficult to install components.

4. Draw the circuit frame of the circuit board: the shortest distance between the frame line and the component pin pad shall not be less than 2 mm (generally 5 mm is reasonable), otherwise it is difficult to cut

5. Element layout principle:

A. General principle: In PCB design, if the circuit system has both digital circuit and analog circuit As well as large current circuits, they must be laid out separately to minimize the coupling between systems. In the same type of circuit, components must be placed in blocks and zones according to the signal flow direction and function.

B. Component placement direction: components can only be arranged in horizontal and vertical directions, otherwise they cannot be placed in plug-ins.

C. When the potential difference between elements is large, the element spacing shall be large enough to prevent discharge.

D. Input signal processing unit and output signal driving element shall be close to the circuit board edge to make input and output signal lines as short as possible to reduce input and output interference.

E. Element spacing For medium density boards, the spacing between small components, such as small power resistors, capacitors, diodes, and equal split components is related to the plug-in and welding process. During wave soldering, the component spacing can be 50-100 MIL (1.27 – 2.54 mm), which can be larger manually. For example, if 100 MIL is selected, the component spacing is generally 100 – 150 MIL for integrated circuit chips.

F. The de coupling capacitor in the IC should be close to the power supply ground wire pin of the chip, otherwise the filtering effect will become worse In the digital circuit, in order to ensure the reliable operation of the digital circuit system, the IC decoupling capacitor is placed between the power supply and the ground of each digital integrated circuit chip. The decoupling capacitor is generally a ceramic chip capacitor, and the capacity of 0.01~0.1UF decoupling capacitor is generally selected according to the reciprocal of the system operating frequency F In addition, a 10UF capacitor and a 0.01UF ceramic chip capacitor shall be connected between the power line and the ground wire at the inlet of the circuit power supply.

G. The clock circuit component shall be close to the clock signal pin of the single chip microcomputer chip as far as possible to reduce the connection length of the clock circuit, and it is better not to run the line below.

What are the problems in the manufacturing process of multilayer circuit boards

1、 Circuit deformation caused by poor etching of multilayer circuit board

When etching the outer circuit of a multilayer circuit board, if the copper foil edges are deep into the resin on the board surface, there may still be residual copper in the dense circuit area after etching. These phenomena may not be easily detected after etching, but after the nickel leaching process, deformed lines or metal areas may be found on the circuit or the edge of the solder pad. This problem is sometimes considered as a problem of residue or poor washing, but it is actually a problem of circuit etching or improper selection of copper sheet.

2、 Copper exposed on gold surface due to poor tin stripping

For tin stripping after etching, attention must be paid to whether there are still light gray intermediate metals left to be stripped. If it is not completely removed, brushing, pickling and micro etching may not be completely removed, which will inhibit the start of nickel leaching reaction. If the reaction cannot be started completely, copper leakage may occur on the gold plating surface.

3、 Problems of residual copper on the wall of copper free through-hole

At present, the practice of copper free through-hole is mainly to remove the copper by etching after overall copper plating, or to remove the copper by etching after the hole covering process does not allow the hole to be plated with tin. However, the etching solution has no way to remove palladium, so nickel gold will still be adsorbed on the pore wall during the process. This is a direct problem for the products with metal free hole walls.

At present, some multilayer circuit board manufacturers have introduced the so-called chemical copper process without the problem of nickel leaching gold. In fact, the simple way is to reduce the concentration of palladium metal. By this way, subsequent nickel gold plating cannot be started quickly, so it can reduce the problem of making copper free through-hole. However, this approach will lead to the potential crisis of insufficient chemical copper activity and hole breaking, and the scope of chemical copper operation will be narrowed. Some manufacturers also adopt the method of palladium removal by adding palladium removal liquid medicine treatment after stripping the tin bath. However, in the current process, the setting of liquid medicine bath must be increased, and the operating cost will also increase.

At the same time, most of the palladium removal systems will have the risk of corroding copper, while some so-called special Yao water has the problem of patent and cost. Another method is to passivate the palladium layer in the hole with mercaptan solution before tin stripping, so that the subsequent nickel leaching process cannot work. However, if the mercaptan treatment is not cleaned, the residue will be brought into the tin stripping bath and the copper surface will be stained with sulfide. The sulfur on the copper surface is the fatal injury of nickel reaction, so it is very difficult to prevent copper exposure. Therefore, the exact solution for copper free through-hole is still under development.

PCB manufacturers, PCB designers and PCBA processors will explain the oxidation analysis of gilded PCB and the problems of multi-layer PCB.