This paper mainly discusses signal integrity design issues that need to be considered in gigabit data transmission, and introduces the methods of using PCB design tools to solve these problems, such as skin effect and dielectric loss, influence of holes and connectors, differential signal and wiring considerations, power distribution and EMI control, etc.

The rapid development of communication and computer technology has brought high-speed PCB design into the field of gigabit. New high-speed device applications make it possible to transmit such high rates over long distances on backplanes and boards, but at the same time, signal integrity (SI), power integrity, and electromagnetic compatibility problems in PCB design become more prominent.

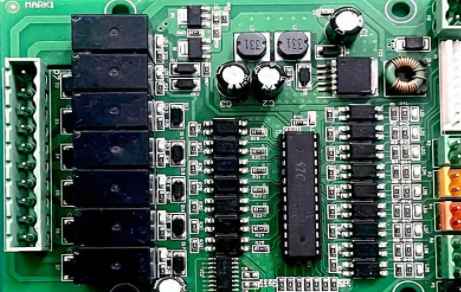

Signal integrity refers to the quality of signal transmission on the signal line. The main problems include reflection, oscillation, timing, ground elastic and crosstalk. Poor signal integrity is not caused by a single factor, but by multiple factors in board design. In the design of PCB boards for gigabit devices, a good signal integrity design requires the engineer to consider all aspects of the device, transmission line interconnection scheme, power distribution, and EMC.

High-speed PCB design EDA tools have evolved from simple simulation verification to a combination of design and verification, helping designers set rules early in the design to avoid errors rather than finding problems later in the design. As the data rate becomes higher and the design becomes more complex, high-speed PCB system analysis tools become more necessary, such as timing analysis, signal integrity analysis, design space parameter scanning analysis, EMC design, power system stability analysis, etc. Here we will focus on some issues that should be considered in signal integrity analysis of PCB design for gigabit equipment.

High-speed devices and device models

Although the gigabit sending and receiving component suppliers will provide the design data related to the chip, there is a process for the device suppliers to understand the signal integrity of new devices, so the design guidelines given by the device suppliers may not be mature, and the design constraints given by the device suppliers are usually very harsh. It can be very difficult for design engineers to meet all the design rules. Therefore, signal integrity engineers are required to use simulation analysis tools to analyze supplier constraint rules and actual design, investigate and optimize component selection, topology structure, matching scheme, and value of matching components, and finally develop PCB layout and routing rules to ensure signal integrity. Therefore, the accurate simulation analysis of gigabit signal becomes very important, and the function of device model in signal integrity analysis is paid more and more attention.

Component models usually include IBIS models and Spice models. Because the board level simulation only cares about the signal response from the output pin through the interconnected system to the input pin, and IC manufacturers do not want to leak the detailed circuit information inside the device, and the simulation time of the transistor-level Spice model is often unbearable, the IBIS model is gradually accepted by more and more device manufacturers and signal integrity engineers in the field of high-speed PCB design.

For the simulation of PCB systems for gigabit devices, engineers often question the accuracy of IBIS models. When the device works in the saturation and cut-off region of the transistor, the IBIS model lacks enough detailed information to describe. In the nonlinear region of the transient response, the simulation results of the IBIS model cannot produce accurate response information as the transistor-level model. However, for ECL type devices, the IBIS model can be obtained in good agreement with the simulation results of the transistor level model, the reason is very simple, ECL driver works in the linear region of the transistor, the output waveform is closer to the ideal waveform, according to the IBIS standard can be more accurate IBIS model.

With the increase of data transmission rate, differential devices developed on the basis of ECL technology have been greatly developed. LVDS standard and CML make gigabit signal transmission possible. From the above discussion, it can be seen that the IBIS standard is still suitable for the design of gigabit systems because of the circuit structure and the corresponding differential technology application. This is also demonstrated by published articles on the application of IBIS models to 2.5Gbps LVDS and CML designs.